A LSI-Package-Board Concept Planner

3 Major Features

- Early Stage Planning Functions

- Communication Aids With Design History Sharing

- Database Security Protection

Your Benefits

- Creativity And Innovation In Product Concept

- Speeding up Product Launching

- Avoiding Risks of Implementation Failures

Front Loading Is Your Merit

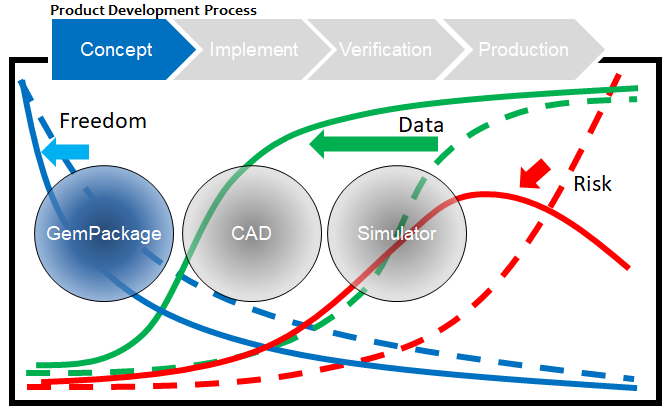

Front loading In electronic product development process is the effort to bring the engineering labors earlier possible to have better product and to launch it to the market earlier possible. The first stage is “concept phase”, traditionally done by one or few veterans in the system house, with the tool “paper, pencil and brain”. This is the most creative phase, starting with the fewest information and producing an innovative product idea, and the output is the data to engage the design phase, such as product size, parts list and netlist. In the concept phase, the biggest problem is that you don’t have enough information to start CAD or simulator to check the doability of your idea. You can check it later but it might be too late to remove the problems with a reasonable time or cost. To alleviate the problem, you can change “paper, pencil and brain” style to “tool and brains” style, e.g. to have a right planner tool to capture the ideas as data, and involve more specialists to share and test the ideas earlier. As the result, you can test more ideas in the middle, find the best idea at last. The risk of failures in later phases is greatly reduced because more ideas tested by the eyes of more specialists.

The merits of the front loading are summarized as follows.

- Enforce creativity and innovation in product concept

- Speeding up the product launching

- Avoiding risks of production failures in later phases

Challenges In Front Loading

To achieve front loading, three parties have their own roles. First, the system house must play the leader role in the co-design team in typical cases. They shall involve necessary partners in earlier phase, and provide them information in early stage. Second party is the semiconductor company. Semiconductor engineers in the team must pay attentions to board level layout from the start, and provide the package/chip layout data to the customer, so that the customer can carry out preliminary simulations in the concept phase. The last one is EDA. EDA needs to support early stage planning functions, with flexible data exchange and communication functions, with security considerations.

Supported Co-Design Types

Semiconductor and electronic products have evolved in the 20th century by introducing the horizontal division of labors. However in 21th century, several factors appeared and the simple don’t-care-beyond-the-boundary strategy does not work anymore. GemPackage supports the four types of co-designs needed today.

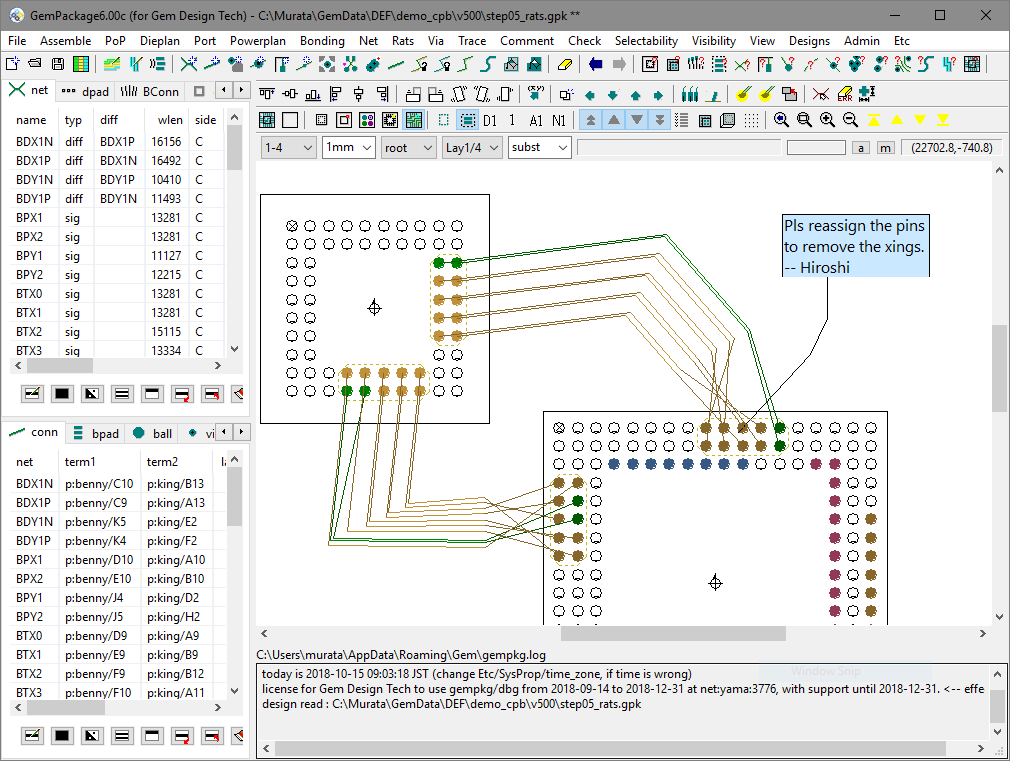

Co-Des I: IC Package Prototyping

System-in-Package and Package-on-Package became popular for IC package structure, after the flip phones and digital still cameras appeared. It brought a sudden increase in IC package design cases. IC package houses supply the major design power, but they usually cannot provide feasibility study service, i.e. determining if the design being possible or not quickly without actually engaging the design. Then the IC package designers in the semiconductor suppliers have to perform the feasibility study themselves. Later, as the the signal speed increase, SI/PI issues are added in the phase, which changed the name from feasibility study to IC package prototyping. GemPackage has proven usefulness for IC package prototyping with the unique rats-bending based routability study function, the user-friendly wire bonding planning function, and many others.

Co-Des II: Chip/Package Co-Design

As the signal become faster and dimmer, the chip does not work correctly if the chip pins are assigned arbitrary and then routed to package pins in a spaghetti-like detoured paths. Dedicated routing techniques have been applied in the IC package and in the mother board, e.g. differential-pair parallel routing and equi-length routing, but they are essentially for local adjustment. In the end, the chip IO designers and the IC package designers should work together to determine the IO placement and IC package routings together. GemPackage has been used for the chip/package co-design because of the IO cell planning feature and the super-hierarchical nature of the database.

Co-Des III: Platform Planning

Signals are getting faster and dimmer further, which makes system houses to face against the problems such as unplanned noise components needed at final stage, or board layout change in a worse case, if they were not careful about their chip. The SI/PI/Thermal simulation have to be adopted but sometimes it is too late because the chip is designed far earlier. To solve the problem, system houses need to start very early board planning for their next generation products, with the next generation ASIC chip. The input information would be not sufficient; some parts are bogus or missing, pin assignments are free, etc. However, if studying well, they become able to ask more specific requests to semiconductor suppliers, for example simulation models, decap requests, and pin assignment, when they actually engage the development of their new chip. GemPackage supports such platform planning, by providing methods for netlist generation based on floorplan (different from traditional netlist based floorplan), considering power integrity far before plane generation, easy-to-use on the fly parts generation, etc.

Co-Des IV: System/Semiconductor Co-Design

Early stage planning, such as platform planning, has been usually done internally in a company. Inter-company collaboration brings new level of benefits. For example, if the system house provide concept phase board layout to semiconductor supplier, the semiconductor supplier can consider it in the initial offer of the pin assignment. If the semiconductor supplier provides the prototype phase IC package layout data to the system house, the system house can simulate SI/PI before the CAD phase. Such big enhancements in the early concept phase realizes a big front loading in your product design process. The merits are (1) innovative products because of the enhanced concept phase, (2) speed-up in product launching, and (3) avoiding risks in later phase. The key to the inter-company co-design in concept phase is in the communication, management, and security issues, rather than in the technical issues. For example, design history is hoped to be shared by all the co-design member companies, but their internal communications have to be hide from others. A company may not want to provide their data if there is no systematic mechanism to prevent unexpected use of the data. GemPackage provides good communication, management, and security functions to support system-house/semiconductor-supplier co-design in concept-phase.

GemPackage: A Concept Planner

A detailed design tool cannot be simply reused as a concept planner, because the functions needed for detailed design and those for concept planning are so different. Concept planner should support the following unique functions, and GemPackage supports them all.

Very Early Stage Planning Functions

The concept phase starts with the fewest information, then EDA must supply functions to start planning from scratch, then it must be able to capture more information seamlessly as the planning evolves. Typical requests are as follows.

- Optimize Floorplan Without Netlist

- Examine Routability Without Actually Routing

- Care Power Integrity WIthout Making Power Planes

- The tool must be useful without much preparation, and it must run in a quick, light, easy, natural and flexible way.

Data Exchange and Communication Aids

EDA has been paying too little about data exchange and communication, comparing to the office tools. The minimum requirements are as follows.

- To communicate with various co-design partners, we need IEEE2401/IEC63055 being fully supported by EDA tools.

- Want to avoid inefficient PC works, such as cutting an EDA tool screen image, pasting it on an office app, adding comments, to exchange ideas with co-design partners.

- Want to share design history with co-design partners, without separately managing spreadsheet documents.

Database Security For Idea Protection

Co-design members cannot share their ideas with other members if their ideas are not protected right, even though they personally wish. NDA is not sufficient in real life. More systematic mechanism is necessary. The requests are as follows.

- Hide Internal Records In Design History Sharing

- Prohibit Unexpected Use In Database Sharing

Demo Request

Please feel free to ask us a free demo of GemPackage, in the following.